16 Мбит DataFlash AT45DB161D |

скачать

скачатьв pdf |

1 Описание

AT45DB161D - микросхема Flash-памяти последовательного доступа с питанием 2.5В или 2.7В. Идеально подходит для хранения цифрового звука и изображений, программного кода и данных. AT45DB161D поддерживает последовательный SPI-подобный интерфейс Atmel RapidS, работающий на скоростях до 66МГц. 17301504 бита памяти сгруппированы в 4096 страницы размером 512/528 байт . В дополнение к основной памяти, AT45DB161D содержит 2 SRAM буфера размером 512/528 байт. Они позволяют принимать данные во время записи в основную память, организовать запись непрерывного потока данных. Встроенная операция чтение-модификация-запись позволяет легко эмулировать EEPROM.

В отличие от микросхем Flash с параллельным интерфейсом, последовательный интерфейс значительно сокращает количество активных выводов, облегчает размещение микросхемы на плате, увеличивает надежность и уровень электромагнитной совместимости. Микросхема оптимальна в задачах, где важны высокая плотность монтажа, низкие напряжение питания и энергопотребление.

AT45DB161D не требует высокого напряжения для записи, поэтому легко реализовать ее перезапись «в системе». В режимах чтения и записи работает от одного источника питания 2.5В - 3.6В, либо 2.7В - 3.6В. AT45DB161D активируется сигналом CS и управляется 3-х проводным интерфейсом из сигналов SI, SO, SCK.

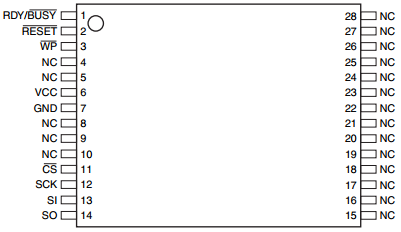

2 Расположение выводов и их назначение

Рисунок 2.1 TSOP тип 1, вид сверху

|

Рисунок 2.2 BGA вид сверху

|

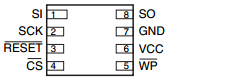

Рисунок 2.3 MLF (VDFN) вид сверху

|

Рисунок 2.4 SOIC вид сверху

|

| Обозначение | Название и выполняемая функция | Активный уровень | Тип |

| CS |

Выбор микросхемы. Активное состояние сигнала

активирует микросхему.

При неактивном CS микросхема переходит в режим ожидания, вывод SO

переводится в высокоимпедансное состояние, данные на выводе SI не

принимаются.

Для начала работы с микросхемой требуется переход CS из высокого в низкое состояние. Чтобы завершить работу требуется переход CS из низкого в высокое. Если завершается операция с внутренним самотактированием (например программирование или цикл стирания), микросхема перейдет в режим ожидания только после ее окончания. |

низкий | Вход |

| SCK | Тактовый сигнал. Используется для тактирования микросхемы и управления исходящим/входящим потоком данных. Информация на выводе SI всегда считывается по нарастающему фронту SCK, а выводится всегда по спадающему фронту SCK. | - | Вход |

| SI | Вход последовательного интерфейса. SI используется для подачи всех данных в микросхему (включая команды и адреса). Данные на выводе SI всегда считываются на нарастающем фронте SCK. | - | Вход |

| SO | Выход последовательного интерфейса. SO используется для выдачи данных из микросхемы. Данные на вывод SO подаются по спадающему фронту SCK. | - | Выход |

| WP |

Защита от записи. В активном состоянии WP все сектора, указанные

в регистре Защита Секторов, будут защищены от

записи и стирания независимо от того была-ли подана или нет

команда Включить Защиту Сектора. Вывод WP работает независимо от

программного управления защитой. В активном состоянии WP

не может меняться содержимое регистра Защита Секторов.

Если при активном WP будет подана команда записи/стирания, микросхема проигнорирует команду и перейдет в состояние ожидания сразу как только CS станет неактивным. При активном WP распознаются команды Включить Защиту Сектора и Заблокировать Сектор. Вывод WP имеет внутреннюю подтяжку вверх и может быть оставлен не соединенным в случае если не используется аппаратное управление защитой. Тем не менее, рекомендуется, там где это возможно, подключать WP к выводу Vcc. |

низкий | Вход |

| RESET |

Сброс. Активное состояние вывода RESET завершит

выполняемую операцию и остановит внутреннюю машину состояний.

Микросхема будет находится в состоянии сброс пока активен RESET.

В микросхеме есть внутренняя схема сброса по подаче питания, поэтому на состояние RESET во время подачи питания не накладываются какие-либо ограничения. Если вывод RESET не задействован рекомендуется подтянуть его вверх. |

низкий | Вход |

| RDY/BUSY | Готов/Занят. Этот вывод с открытым стоком переходит в низкое состояние если выполняет внутреннюю самотактируемую операцию. Обычно, этот вывод находится в высоком состоянии (через внешнюю подтяжку вверх) и переводится в низкое состояние при выполнении операций записи/стирания, сравнения и передачи страницы во внутренний буфер. | - | Выход |

| Vcc | Источник питания. Работа при некорректных значениях Vcc может привести к ошибкам. | - | Питание |

| GND | 0 источника питания. Должен быть подключен к земле системы. | - | Земля |

3 Блок-схема

4 Массив памяти

Для максимальной гибкости в массиве памяти AT45DB161D реализованы три уровня разбиения: по секторам, по блокам и по страницам. Эти уровни, а также количество страниц в секторе и блоке изображены на рисунке «Архитектура памяти». Все операции записи выполняются на страничном уровне, операции стирания на уровне всей микросхемы, сектора, блока или страницы.

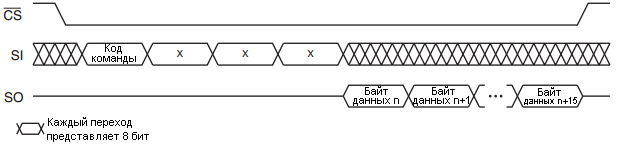

5 Работа с микросхемой

Микросхема управляется командами от ведущего процессора. Список команд и соответствующие им коды указаны в таблицах 15.1-15.7. Команда начинается спадающим фронтом сигнала CS, следом идут 8-битный код команды, номер буфера или адрес в массиве памяти. Подача тактового сигнала на SCK при активном CS, приводит к чтению с вывода SI кода команды, номера буфера или адреса в массиве памяти. Коды команд, адреса и данные передаются старшим битом вперед (MSB).

В этом документе, в случае если размер страницы равен 528 байт, для обозначения адреса в буфере используются символы BFA9-BFA0. Символами PA11-PA0 обозначен адрес страницы в массиве памяти, а символами BA9-BA0 адрес байта внутри страницы.

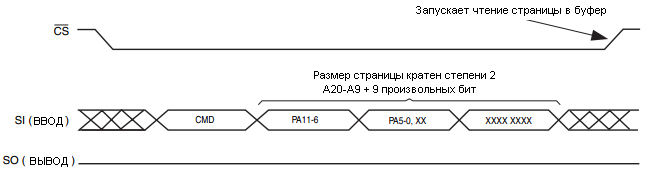

Если размер страницы 512 байт, для обозначения адреса в буфере используются символы BFA9-BFA0. А для адресации в массиве памяти A20-A0, где A20-A9 задают адрес страницы, A8-A0 задают адрес байта внутри страницы.

6 Команды чтения

Данные можно прочитать из основной памяти или любого из 2-х встроенных SRAM-буферов подачей соответствующих команд.

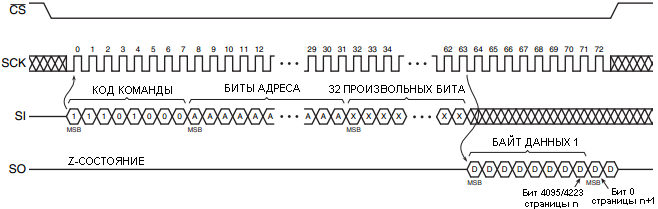

6.1 Непрерывное чтение массива(устаревшая команда E8H): до 66МГц

Команда «Непрерывное чтение массива» применяется при чтении данных непрерывным потоком, подачей лишь тактового сигнала. Достаточно подать код команды и начальный адрес в массиве памяти, указание дополнительной адресной информации или управляющих сигналов не требуется. В DataFlash содержится встроенный счетчик адреса, который автоматически увеличивается с каждым тактовым импульсом. Указав начальный адрес в массиве и подав команду «Непрерывное чтение массива». Подачей только тактового сигнала можно организовать непрерывный поток данных с микросхемы.

Для чтения страниц стандартного размера (528 байт), необходимо подать команду E8, после которой следуют 3 адресных байта (формируют 24 бита адреса страницы и байта) и 4 произвольных байта. Первые 12 бит(PA11-PA0) 22-битной адресной последовательности задают номер читаемой страницы в массиве, а последние 10бит(BA9-BA0) стартовый байт внутри страницы.

Для чтения страниц размером 512 байт, необходимо подать команду E8, после которой следуют 3 адресных байта (формируют 24 бита адреса страницы и байта) и 4 произвольных байта. Первые 12 бит(A20-A9) 22-битной адресной последовательности задают номер читаемой страницы в массиве, а оставшиеся 9 бит(A8-A0) стартовый байт внутри страницы.

Произвольные байты, которые подаются после адресных, инициализируют функцию чтения. Тактовые импульсы на выводе SCK, следующие после 4-х произвольных байт, приведут к выдаче данных на выводе SO.

Вывод CS должен оставаться в низком состоянии во время загрузки кода команды, адресных байт, произвольных байт и чтения данных. Если во время чтения будет достигнут конец страницы, микросхема продолжит чтение с начала следующей страницы без каких-либо задержек связанных с пересечением границ. Если будет прочтен последний байт массива памяти, чтение продолжиться с начала первой страницы, задержек так же не будет.

Переход вывода CS из низкого состояния в высокое завершит операцию чтения и переведет вывод SO в третье состояние. Максимальная частота SCK для непрерывного чтения определяется параметром fcar1. Команда непрерывного чтения не меняет содержимое внутренних SRAM-буферов.

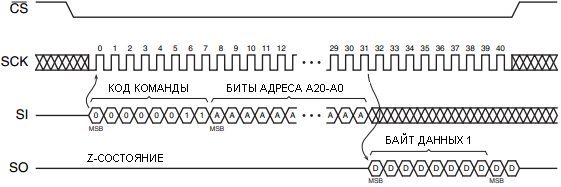

6.2 Непрерывное чтение массива(высокоскоростное: 0BH): до 66МГц

Эта команда применяется при последовательном чтении массива основной памяти последовательным интерфейсом с частотой тактового сигнала вплоть до максимальной, определяемой параметром fcar1.

Для чтения страниц стандартного размера (528 байт) необходимо сначала активировать сигнал CS, потом подать команду 0B, после которой следуют 3 адресных байта (формируют 24 бита адреса страницы и байта) и 1 произвольный. Первые 12 бит(PA11-PA0) 22-битной адресной последовательности задают номер читаемой страницы в массиве, а последние 10 бит(BA9-BA0) стартовый байт внутри страницы.

Для чтения страниц размером 512 байт необходимо подать команду 0B, после которой следуют 3 адресных байта (A20-A0) и 1 произвольный. Тактовые импульсы на выводе SCK, следующие после произвольного байта, приведут к выдаче данных на выводе SO.

Вывод CS должен оставаться в низком состоянии во время загрузки кода команды, адресных байт, произвольного байта и чтения данных. Если во время чтения будет достигнут конец страницы, микросхема продолжит чтение с начала следующей страницы без каких-либо задержек связанных с пересечением границ. Если будет прочтен последний байт массива памяти, чтение продолжиться с начала первой страницы, задержек так же не будет.

Переход вывода CS из низкого состояния в высокое завершит операцию чтения и переведет вывод SO в третье состояние. Максимальная частота SCK для непрерывного чтения определяется параметром fcar1. Команда непрерывного чтения не меняет содержимое внутренних SRAM-буферов.

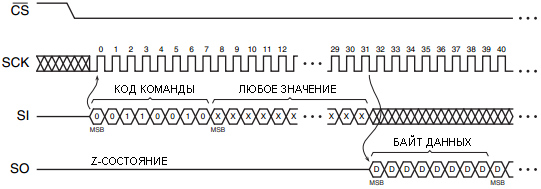

6.3 Непрерывное чтение массива(низкоскоростное 03H):до 33МГц

Эта команда применяется для последовательного чтения массива основной памяти без подачи произвольных байт интерфейсом с частотой тактового сигнала вплоть до максимальной, определяемой параметром fcar2.

Для чтения страниц стандартного размера (528 байт) необходимо сначала активировать сигнал CS, потом подать команду 03, после которой следуют 3 адресных байта (формируют 24 бита адреса страницы и байта). Первые 12 бит (PA11-PA0) 22-битной адресной последовательности задают номер читаемой страницы в массиве, а последние 10 бит(BA9-BA0) стартовый байт внутри страницы.

Для чтения страниц размером 512 байт необходимо подать команду 03, после которой следуют 3 адресных байта (A20-A0). Тактовые импульсы на выводе SCK, следующие после адресных байт,приведут к выдаче данных на выводе SO.

Вывод CS должен оставаться в низком состоянии во время загрузки кода команды, адресных байт и чтения данных. Если во время чтения будет достигнут конец страницы, микросхема продолжит чтение с начала следующей страницы без каких-либо задержек связанных с пересечением границ. Если будет прочтен последний байт массива памяти, чтение продолжиться с начала первой страницы, задержек так же не будет.

Переход вывода CS из низкого состояния в высокое завершит операцию чтения и переведет вывод SO в третье состояние. Команда непрерывного чтения не меняет содержимое внутренних SRAM-буферов.

6.4 Чтение страницы основной памяти

Команда Чтение Страницы Основной Памяти позволяет прочесть данные напрямую из одной из 4096 страниц основной памяти, минуя оба внутренних буфера, сохраняя содержимое этих буферов неизменным. Чтобы начать чтение страницы стандартного размера (528 байт), необходимо подать в микросхему команду D2H, 3 байта адреса (формируют 24 бита адреса страницы и байта) и 4 произвольных байта. Первые 12 бит(PA11-PA0) 22-битной адресной последовательности задают номер читаемой страницы в массиве, а последние 10 бит(BA9-BA0) стартовый байт внутри страницы. Чтобы начать чтение страницы размером 512 байт необходимо подать в микросхему команду D2H, 3 байта адреса (формируют 24 бита адреса страницы и байта) и 4 произвольных байта. Первые 12 бит(A20-A9) 21-битной адресной последовательности задают номер читаемой страницы в массиве, а последние 9 бит(A8-A0) стартовый байт внутри страницы.

Произвольны байты, которые подаются после адресных, инициализируют функцию чтения. Тактовые импульсы на выводе SCK, следующие после 4-х произвольных байт, приведут к выдаче данных на выводе SO.

Вывод CS должен оставаться в низком состоянии во время загрузки кода команды, адресных байт и чтения данных. Если во время чтения будет достигнут конец страницы, микросхема продолжит чтение с начала этой же страницы.

Переход вывода CS из низкого состояния в высокое завершит операцию чтения и переведет вывод SO в третье состояние. Максимальная частота SCK при чтении страницы основной памяти определяется параметром fSCK. Команда не меняет содержимое внутренних SRAM-буферов.

6.5 Чтение буфера

Доступ к внутренним SRAM буферам можно получить независимо от массива основной памяти. Команда Чтение Буфера позволяет читать данные непосредственно из внутренних SRAM буферов. Для чтения используются 4 кода операции D4H и D1H для буфера 1, и D6H и D3H для буфера 2. Выбор конкретного кода операции зависит от максимальной частоты SCK на которой будут считываться данные. Коды D4H и D6H могут быть использованы на любой частоте сигнала SCK вплоть до максимальной, заданной fCAR1. D1H и D3H используются для меньших скоростей чтения, вплоть до максимума заданного fCAR2.

Чтобы прочесть буфер стандартного размера (528 байт) необходимо подать код операции и сопроводить его 3-мя адресными байтами, состоящими из 14 бит произвольного значения и 10 бит адреса в буфере. Чтобы прочесть буфер размером 512 байт после кода операции подают 3 байта, в которых 15 бит не имеют значения и 9 задают адрес внутри буфера. После адресных байт, для инициализации операции чтения, посылают один произвольного значения.

Вывод CS должен оставаться в низком состоянии во время загрузки кода команды, адресных и произвольных байт и чтения данных. Если во время чтения будет достигнут конец буфера, чтение продолжится с его начала.

Переход вывода CS из низкого состояния в высокое завершит операцию чтения и установит вывод SO в третье состояние.

7 Команды записи и стирания

7.1 Запись буфера

Данные, поступающие с входного сигнала SI, могут быть записаны либо в буфер 1 либо в буфер 2. Для записи данных в стандартный буфер (размером 528 байт) необходимо подать однобайтовый код команды 84H для буфера 1 и 87H для буфера 2. После чего подать 3 адресных байта, состоящих из 14 произвольных бит и 10 бит адреса в буфере (BFA1-BFA0). Адресные биты задают первый байт в буфере в который будет выполнена запись. Для записи данных в буфер размером 512 байт, необходимо подать команду 84H для буфера 1 и 87H для буфера 2. После команды подают 3 адресных байта, в которых 15 произвольных и 9 бит адреса в буфере (BFA9-BFA0). Адресные биты задают первый байт в буфере, в который будет выполнена запись. Сразу после адресных байт, с последующими тактовыми импульсами, подают байты данных. Если запись дойдет до границы буфера, микросхема автоматически продолжит запись с его начала. Данные будут загружаться до тех пор, пока не произойдет переход сигнала CS из низкого уровня в высокий.

7.2 Запись буфера в страницу основной памяти с автоматическим стиранием

Данные, находящиеся в буфере 1 или буфере 2, могут быть записаны в основную память микросхемы. Для этого необходимо подать команду 83H для буфера 1 и 86H для буфера 2. При записи в страницы стандартного размера (528 байт), после команды подаются 3 адресных байта в которых 2 произвольных бита, 12 бит (PA11-PA0) задают адрес программируемой страницы в основной памяти , 10 произвольных бит. Чтобы записать в страницы размером 512 байт необходимо подать команду 83H для буфера 1 и 86H для буфера 2. После команды подаются 3 адресных байта в которых 3 произвольных бита, 12 бит (A20-A9) задают адрес программируемой страницы в основной памяти, 9 произвольных бит. Переход сигнала CS из низкого состояния в высокое сначала сотрёт страницу в основной памяти (стертое состояние логическая 1), после чего запишет данные из буфера в указанную страницу основной памяти. Операция стирания и записи страницы самотактируемая и выполняется за максимальное время tEP. В течение этого времени регистр статуса и вывод RDY/BUSY будут информировать о занятости микросхемы.

7.3 Запись буфера в страницу основной памяти без автоматического стирания

Ранее стёртая страница основной памяти может быть запрограммирована содержимым буфера 1 или буфера 2. Для этого необходимо подать команду 88H для буфера 1 и 89H для буфера 2. При записи в страницы стандартного размера (528 байт), после команды подаются 3 адресных байта в которых 2 произвольных бита, 12 бит (PA11-PA0) задают адрес программируемой страницы в основной памяти, 10 произвольных бит. Чтобы записать в страницы размером 512 байт необходимо подать команду 88H для буфера 1 и 89H для буфера 2. После команды подаются 3 адресных байта в которых 3 произвольных бита, 12 бит (A20-A9) задают адрес программируемой страницы в основной памяти, 9 произвольных бит. Переход сигнала CS из низкого состояния в высокое запустит процесс записи данных из буфера в указанную страницу основной памяти. Необходимо чтобы странница основной памяти, в которую будет произведена запись, была предварительно очищена одной из команд стирания(Стирание страницы или Стирание блока). Операция записи страницы самотактируемая и выполняется за максимальное время tP. В течение этого времени регистр статуса и вывод RDY/BUSY будут информировать о занятости микросхемы.

7.4 Стирание страницы

Для стирания любой страницы в основной памяти применяется команда Стирание Страницы. Выполнив команду для какой-либо страницы, мы тем самым разрешаем в дальнейшем выполнить для этой же страницы команду Запись Буфера в Страницу Основной Памяти. Для стирания страницы стандартного размера (528 байт) необходимо подать команду 81H, после чего подать 3 адресных байта,состоящих из 2-х произвольных бит, 12 бит адреса страницы (PA11-PA0) и 10 произвольных бит. Для стирания страницы размером 512 байт необходимо подать команду 81H, после чего подать 3 адресных байта,состоящих из 3-х произвольных бит, 12 бит адреса страницы (A20-A9) и 9 произвольных бит. Переход сигнала CS из низкого состояния в высокое запустит процесс стирания указанной страницы. Операция стирания самотактируемая и выполняется максимум за время tPE. В течение этого времени регистр статуса и вывод RDY/BUSY будут информировать о занятости микросхемы.

7.5 Стирание блока

Можно стереть блок сразу из 8 страниц. Эта команда применяется при записи больших объемов данных. Она избавляет от необходимости вызова нескольких команд Стирание Страницы.

Для стирания блока состоящего из страниц стандартного размера (528 байт) необходимо подать команду 50H, после чего подать 3 адресных байта,состоящих из 2-х произвольных бит, 9 адресных бит (PA11-PA3) и 13 произвольных бит. Для стирания блока из страниц размером 512 байт необходимо подать команду 50H, после чего подать 3 адресных байта,состоящих из 3-х произвольных бит, 9 бит адреса (A20-A12) и 12 произвольных бит. Переход сигнала CS из низкого состояния в высокое запустит процесс стирания указанного блока. Операция стирания самотактируемая и выполняется максимум за время tBE. В это время регистр статуса и вывод RDY/BUSY будут информировать о занятости микросхемы.

Таблица 7.1 Адресация при стирании блока| PA11/A20 | PA10/A19 | PA9/A18 | PA8/A17 | PA7/A16 | PA6/A15 | PA5/A14 | PA4/A13 | PA3/A12 | PA2/A11 | PA1/A10 | PA0/A9 | блок |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | X | X | X | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | X | X | X | 2 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | X | X | X | 3 |

| · | · | · | · | · | · | · | · | · | · | · | · | · |

| · | · | · | · | · | · | · | · | · | · | · | · | · |

| · | · | · | · | · | · | · | · | · | · | · | · | · |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | X | X | X | 508 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | X | X | X | 509 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | X | X | X | 510 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | X | X | X | 511 |

7.6 Стирание сектора

Команда Стирание Сектора может стереть любой сектор основной памяти. В микросхеме есть 16 секторов, только один может быть стёрт в данный момент времени. Для стирания секторов 0a и 0b, при стандартном размере страниц (528 байт), необходимо подать команду 7CH, после чего подаются 3 адресных байта, состоящих из 2-х произвольных бит, 9 бит адреса страницы (PA11-PA3) и 13 произвольных бит. Для стирания секторов 1-15 необходимо подать команду 7CH, после чего подаются 3 адресных байта, состоящих из 2-х произвольных бит, 4 адресных бит страницы(PA11-PA8) и 18 произвольных бит.

Для стирания секторов 0a и 0b, при размере страниц 512байт, необходимо подать команду 7CH, после чего подаются 3 адресных байта, состоящих из 3-х произвольных бит, 9 бит адреса страницы (A20-A12) и 12 произвольных бит. Для стирания секторов 1-15 необходимо подать команду 7CH, после чего подаются 3 адресных байта, состоящих из 3-х произвольных бит, 4 адресных бит страницы(A20-A17) и 17 произвольных бит.

Адресные биты страницы задают любой корректный адрес в границах сектора, который должен быть стерт. Переход сигнала CS из низкого состояния в высокое запустит процесс стирания указанного сектора. Операция стирания самотактируемая и выполняется максимум за время tSE. В это время регистр статуса и вывод RDY/BUSY будут информировать о занятости микросхемы.

Таблица 7.2Адресация при стирании сектора| PA11/A20 | PA10/A19 | PA9/A18 | PA8/A17 | PA7/A16 | PA6/A15 | PA5/A14 | PA4/A13 | PA3/A12 | PA2/A11 | PA1/A10 | PA0/A9 | сектор |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | X | X | X | 0a |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | X | 0b |

| 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | 1 |

| 0 | 0 | 1 | 0 | X | X | X | X | X | X | X | X | 2 |

| · | · | · | · | · | · | · | · | · | · | · | · | · |

| · | · | · | · | · | · | · | · | · | · | · | · | · |

| · | · | · | · | · | · | · | · | · | · | · | · | · |

| 1 | 1 | 0 | 0 | X | X | X | X | X | X | X | X | 12 |

| 1 | 1 | 0 | 1 | X | X | X | X | X | X | X | X | 13 |

| 1 | 1 | 1 | 0 | X | X | X | X | X | X | X | X | 14 |

| 1 | 1 | 1 | 1 | X | X | X | X | X | X | X | X | 15 |

7.7 Стирание микросхемы

Основная память может быть полностью очищена одной командой Стирание Микросхемы. Чтобы ее выполнить необходимо подать последовательность из 4-х байт C7H, 94H, 80H, 9AH. Так как стирается весь массив памяти то нет необходимости в указании адресных байт, поэтому любые данные, поступившие после кода команды, будут проигнорированы. После загрузки последнего байта кода команды, для запуска процесса стирания должен быть деактивирован сигнал CS. Операция стирания самотактируемая и длится tCE. Во время стирания Регистр Статуса будет информировать о том, что микросхема занята.

Команда стирание микросхемы не затрагивает защищенные или заблокированные сектора. Содержимое таких секторов сохраняется.

Таблица 7.3 Команда Стирание Микросхемы| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Стирание Микросхемы | C7H | 94H | 80H | 9AH |

7.8 Запись основной памяти через буфер

Эта команда является комбинацией Записи Буфера, Записи Буфера в Основную Память с Встроенным Стиранием. Сначала данные с вывода SI загружаются в буфер 1 или буфер 2, а потом записываются в указанную страницу основной памяти. Чтобы записать данные через буфер в основную память со стандартным размером страницы (размером 528 байт) необходимо подать однобайтовый код команды 82H для буфера 1 и 85H для буфера 2. После чего подать 3 адресных байта, состоящих из 2-х произвольных бит и 12 бит адреса страницы (PA11-PA0) и 10 адресных бит в буфере (BFA9-BFA0).

Чтобы записать данные через буфер в основную память с размером страницы 512 байт необходимо подать однобайтовый код команды 82H для буфера 1 и 85H для буфера 2. После чего подать 3 адресных байта, состоящих из 3-х произвольных бит и 12 бит адреса страницы (A20-A9) и 9 адресных бит в буфере (BFA8-BFA0).

После получения адресных байт микросхема принимает данные с входного вывода и помещает их в указанный буфер данных. Если запись дойдет до границы буфера, микросхема автоматически продолжит запись с его начала.

Переход вывода CS из низкого состояния в высокое сначала очистит указанную страницу основной памяти, а потом запишет данные из буфера в эту страницу. Обе операции самотактируемые и длятся время tEP. В течение этого времени Регистр Статуса и вывод RDY/BUSY будут информировать о занятости микросхемы.

8 Защита сектора

Есть два способа защиты от ошибочных циклов записи и стирания: аппаратный и программный. Программный метод для включения и выключения защиты сектора использует вызов соответствующих команд, а аппаратный использует вывод Защита от записи(WP). Сектора, которые будут защищены от записи или стирания, указываются в специальном энергонезависимом регистре Защита Секторов. Текущее состояние программного или аппаратного режима защиты секторов можно узнать через Регистр Статуса.

8.1 Программная защита сектора

8.1.1 Включить защиту сектора

Включение защиты от записи или стирания для секторов, указанных в регистре Защита Секторов как защищенные, производится подачей команды Включить Защиту Сектора. Для этого необходимо предварительно активировать сигнал CS. После этого, через вывод SI, подать 4-х байтовый код команды. После загрузки последнего бита в коде команды, деактивация сигнала CS включит защиту сектора.

Таблица 8.1 Команда Включить Защиту Сектора| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Включить Защиту Сектора | 3DH | 2AH | 7FH | A9H |

8.1.2 Выключить защиту сектора

Как и для любой другой команды, чтобы программно выключить защиту сектора необходимо предварительно активировать сигнал CS. После этого, через вывод SI, подать 4-байтовый код команды. После загрузки последнего бита в коде команды, деактивация сигнала CS выключит защиту сектора. Вывод WP должен находится в неактивном состоянии, в противном случае команда Выключить защиту сектора будет проигнорирована.

Таблица 8.2 Команда Выключить Защиту Сектора| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Выключить Защиту Сектора | 3DH | 2AH | 7FH | 9AH |

8.1.3 Несколько замечаний о программной защите секторов

Программная защита секторов применяется если управляющий контроллер не может изменять состояние сигнала WP. В таких случаях вывод WP можно оставить не соединенным (имеется внутренняя подтяжка), а для управления защитой секторов использовать команды Включить Защиту Сектора и Выключить Защиту Сектора.

Если для микросхемы выполнить сброс и повторную подачу питания, то программный режим защиты будет отключен. Как только на микросхему будет подано питание необходимо повторно подать команду Включить защиту сектора.

9 Аппаратная защита

Сектора, указанные в регистре Защита Секторов, а также непосредственно сам этот регистр могут быть защищены от записи или стирания активным состоянием вывода WP. Регистр, любой из защищаемых секторов не могут быть изменены пока WP находится в активном состоянии. Для того чтобы изменить регистр Защита Секторов необходимо деактивировать WP. Если вывод WP постоянно соединен с GND, содержимое регистра изменить будет нельзя, если же WP постоянно соединен с VCC, то содержимое регистра менять можно.

Вывод WP переопределяет программно-управляемую защиту, но только в случае защиты секторов. Например, если сектора не были предварительно защищены командой Включить Защиту Сектора, то просто активировав WP, максимум через время tWPE, включим защиту сектора. Деактивировав WP, отключим защиту секторов (максимум спустя время tWPD), по крайней мере если до или во время активности WP не подавалась команда Включить Защиту Сектора. Если такая команда подавалась, то после деактивации WP защита секторов не отключится. В этом случае, чтобы отключить защиту необходимо, пока вывод WP неактивен, подать команду Выключить Защиту Сектора. Команда Выключить Защиту Сектора игнорируется при активном WP.

Для защиты от случайных изменений состояния вывода WP микросхема имеет встроенный фильтр помех.

В таблице ниже детально описывается состояние защиты секторов в зависимости от различных состояний вывода WP, команды Включить Защиту Сектора и команды Выключить Защиту Сектора.

Рисунок 9.1 Вывод WP и состояние защиты| Момент времени | Вывод WP | Команда Включить Защиту Сектора | Команда Выключить Защиту Сектора | Состояние Защиты | Регистр Защита Секторов |

| 1 | высокий | ранее не подавалась | X | выключено | чтение/запись |

| - | подать | выключено | чтение/запись | ||

| подать команду | - | включено | чтение/запись | ||

| 2 | низкий | X | X | включено | только чтение |

| 3 | высокий | команда подана в момент времени 1 или 2 | еще не подавалась | включено | чтение/запись |

| - | подать | выключено | чтение/запись | ||

| подать команду | - | включено | чтение/запись |

9.1 Регистр защита секторов

Энергонезависимый регистр Защита Секторов задает сектора, которые программным или аппаратным методом будут защищены от записи. Регистр содержит 16 байт данных, значения которых задают состояние защиты для секторов 0..15. Регистр, после предварительного стирания, доступен пользователю для записи. В таблице 9.2 представлен формат данных в регистре Защита Секторов.

Таблица 9.2 Регистр Защита Секторов| Номер сектора | 0(0a, ob) | от 1 до 15 |

| Защищен | См таблицу 9-3 | FFH |

| Не защищен | 00H |

Таблица 9.3. Сектор 0(0a, 0b)

| 0a | 0b | Значение данных | |||

| Страницы 0-7 | Страницы 8-255 | ||||

| Бит 7,6 | Бит 5,4 | Бит 3,2 | Бит 1,0 | ||

| Сектора 0a, 0b не защищены | 00 | 00 | xx | xx | 0xH |

| Защищен сектор 0a | 11 | 00 | xx | xx | CxH |

| Защищен сектор 0b(страницы 8-255) | 00 | 11 | xx | xx | 3xH |

| Защищены сектора 0a(страницы 0-7), 0b(страницы 8-255) | 11 | 11 | xx | xx | FxH |

Примечание:

-

При поставке от Atmel байты 0-15 установлены в значение 00H

x – произвольное значение

9.1.1 Команда очистить регистр защиты секторов

Чтобы изменить значения в регистре Защиты Секторов необходимо сначала очистить его командой Очистить Регистр Защиты Секторов.

Для очистки необходимо, как и с любой другой командой, предварительно активировать сигнал CS. После этого, через вывод SI, подать 4-х байтовый код команды 3DH, 2AH, 7FH, CFH. Как только будет загружен последний бит команды, деактивация сигнала CS запустит самотактируемый цикл стирания. Цикл стирания регистра выполняется за время tPE, в течение которого Регистр Статуса информирует о занятости микросхемы. Если микросхема будет обесточена до завершения цикла очистки, содержимое регистра защиты сектора не предсказуемо.

Содержимое регистра может быть очищено независимо от состояния режима защиты секторов. Так как в очищенном состоянии все байты принимают значение FFH, которое указывает на защиту сектора, то включение режима защиты секторов на время стирания повышает эффективность защиты на случай случайной записи или стирания микросхемы. Если по какой-либо причине, непосредственно сразу после стирания, но перед установкой регистра защиты секторов, будет подана команда записи или стирания сектора или страницы, то ошибочная команда не будет выполнена потому что все сектора будут уже защищены.

Таблица 9.4 Команда Очистить Регистр Защиты Секторов| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Очистить Регистр Защиты Секторов | 3DH | 2AH | 7FH | CFH |

9.1.2 Команда запись регистра защиты секторов

После очистки регистра защиты секторов его можно перепрограммировать командой Запись Регистра Защиты Секторов.

Для записи необходимо сначала активировать сигнал CS, потом подать через вывод SI соответствующий 4-х байтовый код команды 3DH, 2AH, 7FH, FCH. После подачи в микросхему последнего бита кода команды подаётся содержимое регистра защиты секторов. Как уже говорилось в главе 9.1, регистр содержит 16 байт данных, поэтому в микросхему необходимо подавать 16 байт. Первый байт соответствует сектору 0, второй сектору 1 и т.д. до последнего байта, который соответствует сектору 15.

После загрузки последнего байта, для запуска цикла записи необходимо деактивировать сигнал CS. Запись является самотактируемой операцией и выполняется максимум за время tP, в течение которого Регистр Статуса будет информировать о занятости микросхемы. Если микросхема будет обесточена до завершения цикла записи, содержимое регистра защиты секторов не предсказуемо.

Если перед деактивацией сигнала CS было загружено менее 16 байт данных, то состояние защиты для секторов, соответствующих не загруженным данным, будет неопределенным. Например, если загрузили только 2 байта из 16, то состояние защиты для оставшихся 14 секторов неопределенное. Кроме того, если загрузить больше 16 байт, то данные перейдут к началу регистра. Например, если загрузить 17 байт, то 17-ый байт будет соответствовать состоянию сектора 0.

Если в регистр записать значения отличные от 00H и FFH, то состояние защиты соответствующего сектора также не определено. Например, если в позицию 2 регистра записать значение 17H, то состояние защиты для сектора 2 будет неопределенным.

Регистр Защиты Секторов может быть перезаписан независимо от того включена ли защита секторов или нет. Возможность перезаписи регистра во время включенной защиты секторов позволяет пользователю временно отключить защиту только для некоторых секторов, а не для всех сразу.

Для выполнения команды задействован внутренний SRAM-буфер 1, поэтому содержимое буфера 1 до и после выполнения команды будет отличаться.

Таблица 9.5 Команда Запись Регистра Защиты Сектора| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Запись Регистра Защиты Сектора | 3DH | 2AH | 7FH | FCH |

9.1.3 Команда чтение регистра защиты секторов

Чтобы прочесть Регистр Защиты Секторов необходимо предварительно активировать сигнал CS. После чего, через вывод SI, подать код команды 32H и три произвольных байта. После подачи кода команды и трех произвольных байт все последующие тактовые импульсы на выводе SCK приведут к выдаче на выводе SO содержимого регистра. Первый байт соответствует сектору 0(0a, 0b), второй соответствует сектору 1, последний (16-ый байт) соответствует сектору 15. Все последующие тактовые импульсы приведут к выдаче произвольных данных. Для прекращения чтения регистра и перевода выхода SO в высокоимпедансное состояние необходимо деактивировать сигнал CS.

Таблица 9.6 Команда Чтение Регистра Защиты Сектора| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Чтение Регистра Защиты Сектора | 32H | xxH | xxH | xxH |

Примечание: xx = Произвольный Байт

Рисунок 9.4 Чтение Регистра Защиты Сектора

9.1.4 Несколько замечаний о регистре защиты секторов

Регистр Защиты Секторов имеет ограничение на 10000 циклов записи/стирания. Пользователи должны тщательно оценивать количество изменений регистра защиты за весь жизненный цикл конечного продукта. Если требуется более 10000 изменений, вызванных временными отключениями защиты для избранных секторов, то необходимо ограничить подобную практику. Вместо этого, чтобы не превысить ограничение в 10000 циклов, можно использовать комбинацию из временного отключения защиты избранных секторов и полного отключения защиты.

10 Функции защиты

10.1 Блокировка сектора

В микросхеме реализован механизм Блокировки Сектора, который навсегда переводит любой сектор в доступный только для чтения. Эта функция требуется в приложениях, которым необходима возможность защитить несколько секторов от злоумышленных попыток изменить программный код или информацию защиты. Однажды заблокированный сектор более никогда не сможет быть стерт или перезаписан, а также разблокирован.

Как и для любой другой команды, чтобы выполнить блокировку сектора необходимо сначала активировать сигнал CS. После этого в строго заданном порядке послать 4-х байтовый код команды 3DH, 2AH, 7FH и 30H. После кода команды следуют 3 адресных байта, указывающих любой адрес в границах блокируемого сектора. Далее, для запуска самотактируемого процесса блокировки, необходимо деактивировать сигнал CS.

Процесс блокировки должен закончится максимум за время tP, в течение которого Регистр Статуса будет информировать о занятости микросхемы. Если во время выполнения блокировки микросхема будет обесточена, то блокировка сектора не гарантируется. В этом случае, чтобы определить состояние блокировки сектора, рекомендуется прочесть содержимое регистра блокировки и при необходимости подать команду снова.

Таблица 10.1Блокировка Сектора| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Блокировка Сектора | 3DH | 2AH | 7FH | 30H |

10.1.1 Регистр блокировки секторов

Регистр Блокировки Секторов это энергонезависимый регистр содержащий 16 байт данных:

Таблица 10.2 Регистр Блокировки Секторов| Номер сектора | 0(0a, ob) | от 1 до 15 |

| Заблокирован | См таблицу 10-3 | FFH |

| Не заблокирован | 00H |

| 0a | 0b | Бит 3,2 | Бит 1,0 | Значение данных | |

| Страницы 0-7 | Страницы 8-255 | ||||

| Бит 7,6 | Бит 5,4 | ||||

| Сектора 0a, 0b не заблокированы | 00 | 00 | 00 | 00 | 00xH |

| Заблокирован сектор 0a | 11 | 00 | 00 | 00 | C0xH |

| Заблокирован сектор 0b | 00 | 11 | 00 | 00 | 30xH |

| Заблокированы сектора 0a(страницы 0-7), 0b(страницы 8-255) | 11 | 11 | 00 | 00 | F0xH |

10.1.2 Чтение регистра блокировки секторов

Регистр Блокировки Секторов может быть прочитан для того чтобы определить какие из секторов заблокированы. Для чтения необходимо предварительно активировать сигнал CS, после чего подать через вывод SI код команды 35H и 3 произвольных байта. После подачи последнего бита кода команды на вывод SO будет подано содержимое регистра. Первый байт соответствует сектору 0(0a, 0b), второй соответствует сектору 1, последний(16-ый байт) соответствует сектору 15. Последующие тактовые импульсы приведут к выдаче произвольных данных.

Деактивация сигнала CS приведет к завершению чтения регистра и переводу вывода SO в высокоимпедансное состояние.

Таблица 10.4 Команда Чтение Регистра Блокировки Сектора| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Чтение Регистра Блокировки Сектора | 35H | xxH | xxH | xxH |

Примечание: xx = Произвольный Байт

Рисунок 10.2 Чтение Регистра Блокировки Сектора

10.2 Регистр защиты

В микросхеме встроен специализированный регистр, который может использоваться для хранения уникальных серийных номеров или заблокированных ключей. Регистр состоит из 128 байт, которые разделены на 2 части. Первые 64 байт (от 0 до 63) регистра распределены под однократно-записываемое пространство доступное пользователю. После записи этих 64 байт, перезаписать их будет нельзя. Оставшиеся 64 байта регистра записаны компанией Atmel и являются уникальными для каждой микросхемы. Данные записанные на фабрике фиксированы и не могут быть изменены.

Таблица 10.5 Регистр Защиты| Номер байта в регистре защиты | ||||||||||

| 0 | 1 | ... | 62 | 63 | 64 | 65 | ... | 126 | 127 | |

| Тип данных | Однократно записывает пользователь | Записаны на фабрике Atmel | ||||||||

10.2.1 Запись регистра защиты

Часть доступная на запись пользователем не требует предварительного стирания перед записью.

Чтобы записать Регистр Защиты необходимо сначала активировать сигнал CS. После этого, в строго заданном порядке, послать 4-х байтовый код команды 9BH, 00H, 00H и 00H. После подачи в микросхему кода команды подается содержимое программируемой 64-байтной области регистра.

После загрузки последнего байта деактивация сигнала CS запустит самотактируемый процесс записи. Запись регистра должна закончится максимум за время tP, в течение которого Регистр Статуса будет информировать о занятости микросхемы. Если во время процесса записи микросхема будет обесточена, то содержимое программируемой области непредсказуемо.

Если сигнал CS деактивирован до того как будет загружено содержимое всех 64 байт, то в значения незагруженных байт будет непредсказуемым. Например, если загружены только первые 2 байта из 64, то содержимое оставшихся 62 будет неопределенным. Если же будет загружено больше 64 байт, то произойдет переход к началу регистра. Например, если загрузить 65 байт данных, то 65-ый байт будет размещен в позиции 0 Регистра Защиты.

Содержимое программируемой пользователем области может быть записано только единожды. Поэтому нельзя сначала записать только первые два байта, а потом оставшиеся 62.

Команда Запись Регистра Защиты задействует внутренний SRAM-буфер 1, поэтому содержимое буфера 1 до и после выполнения команды будет отличаться.

Рисунок 10.3 Запись Регистра Защиты

10.2.2 Чтение регистра защиты

Регистр Защиты может быть прочтен активацией сигнала CS и последующей подачей кода команды 77H и 3 произвольных байта. После загрузки последнего бита 3-го произвольного байта, на вывод SO будет подано содержимое регистра. Если после чтения последнего байта регистра защиты продолжить подачу тактовых импульсов на вывод SCK, то на SO поступят произвольные данные.

Деактивация сигнала CS завершает чтение регистра и переводит вывод SO в высокоимпедансное состояние.

Рисунок 10.4 Чтение Регистра Защиты

11 Дополнительные команды

11.1 Передача основной страницы в буфер

Страница данных может быть передана из основной памяти в буфер 1 или буфер 2. Для запуска команды, в случае страниц Atmel DataFlash стандартного размера (528 байт), необходимо подать в микросхему 1-байтовый код команды 53H для буфера 1 и 55H для буфера 2, после чего подать 3 адресных байта, состоящих из 2-х случайных бит, 12 бит адреса страницы (PA11-PA0) и еще 10 случайных бит. Для запуска команды, в случае страниц Atmel DataFlash с размером кратным степени 2 (512 байт), необходимо подать в микросхему 1-байтовый код команды 53H для буфера 1 и 55H для буфера 2, после чего подать 3 адресных байта, состоящих из 3-х случайных бит, 12 бит адреса страницы (A20-A9) и еще 9 случайных бит. Во время загрузки кода команды и адресных байт вывод CS должен находится в низком состоянии. Передача страницы данных из основной памяти в буфер начнется с переходом вывода CS из низкого состояния в высокое. Завершение передачи страницы данных (tXFR) определяется чтением регистра статуса или отслеживанием вывода RDY/BUSY.

11.2 Сравнение страницы основной памяти и буфера

Страницу основной памяти можно сравнить с данными в буфере 1 или буфере 2. Чтобы сравнить страницы Atmel DataFlash стандартного размера (528 байт) необходимо подать в микросхему 1-байтовый код команды 60H для буфера 1 и 61H для буфера 2, после чего подать 3 адресных байта, состоящих из 2-х случайных бит, 12 бит адреса страницы (PA11-PA0) и еще 10 случайных бит. Чтобы сравнить страницы Atmel DataFlash с размером кратным степени 2 (512 байт) необходимо подать в микросхему 1-байтовый код команды 60H для буфера 1 и 61H для буфера 2, после чего подать 3 адресных байта, состоящих из 3-х случайных бит, 12 бит адреса страницы (A20-A9) и еще 9 случайных бит. Во время загрузки кода команды и адресных байт вывод CS должен находится в низком состоянии. Сравнение указанной страницы и данных в буфере 1 или буфере 2 начнется с переходом сигнала CS из низкого состояния в высокое. Во время выполнения команды (tCOMP) регистр статуса и вывод RDY/BUSY будут информировать о занятости микросхемы. По завершению команды результат сравнения будет помещен в бит 6 регистра статуса.

11.3 Автоматическая перезапись страницы

Этот режим применим в случае множественных изменений в странице или множественных изменений страниц в секторе. Он является комбинацией 2-х команд: Передача Страницы Основной Памяти в Буфер и Запись Буфера в Страницу Основной Памяти с Автоматическим Стиранием. Страница данных сначала помещается в буфер 1 или буфер 2, после чего те-же самые данные (из буфера 1 или буфера 2) записываются назад в исходную страницу основной памяти. Чтобы запустить операцию для страниц Atmel DataFlash стандартного размера (528 байт) необходимо подать в микросхему 1-байтовый код команды 58H для буфера 1 и 59H для буфера 2, после чего подать 3 адресных байта, состоящих из 2-х случайных бит, 12 бит адреса страницы (PA11-PA0) и еще 10 случайных бит. Чтобы запустить операцию для страниц Atmel DataFlash с размером кратным степени 2 (512 байт) необходимо подать в микросхему 1-байтовый код команды 60H для буфера 1 и 61H для буфера 2, после чего подать 3 адресных байта, состоящих из 3-х случайных бит, 12 бит адреса страницы (A20-A9) и еще 9 случайных бит. Переход сигнала CS из низкого состояния в высокое сначала передаст данные из страницы основной памяти в буфер после чего запишет данные из буфера в ту же самую страницу основной памяти. Операция является самотактируемой и должна завершиться максимум за время tEP. Во время выполнения операции регистр статуса и сигнал RDY/BUSY будут информировать о занятости микросхемы.

Если сектор программируется или перепрограммируется последовательно страница за страницей, то рекомендуется применять алгоритм записи, показанный на рисунке 25.1. Иначе, если записываются несколько байт в странице или хаотично несколько страниц в секторе, то рекомендуется применять алгоритм записи, показанный на рисунке 25.2. Каждая страница в пределах сектора должна быть перезаписана хотя-бы раз за 20000 суммарных операций чтения/записи для этого сектора.

11.4 Чтение регистра статуса

Регистр статуса может быть применён для определения готовности/занятости микросхемы, результата сравнения страницы основной памяти с буфером, статуса защиты сектора, емкости микросхемы. Регистр статуса можно прочесть в любой момент времени, даже во время выполнения самотактируемых операций записи и стирания. Чтобы прочесть регистр статуса необходимо активировать сигнал CS, после чего загрузить код команды D7H. После загрузки кода команды, с последующими тактовыми импульсами, на выводе SO будет выдан 1-байтовый регистр статуса. После передачи одного байта регистра статуса, в случае активного CS и последующих тактовых импульсах, выдача повторится. Данные в регистре статуса постоянно обновляются, поэтому все повторные выдачи будут содержать новые данные.

Состояние готов/занят соответствует биту 7 в регистре статуса. Если бит 7 равен 1, то микросхема не занята и готова к приему следующей команды. Если бит 7 равен 0, микросхема занята. Есть несколько команд, которые переводят микросхему в состояние занят: Передача Страницы Основной Памяти в Буфер, Сравнение Страницы Основной Памяти с Буфером, Запись Буфера в Страницу Основной Памяти, Запись Страницы Основной Памяти через Буфер, Стирание Страницы, Стирание Блока, Стирание Сектора, Стирание Микросхемы и Автоматическая Перезапись Страницы.

Результат последней команды Сравнить Страницу Основной Памяти с Буфером отображается в бите 6 регистра статуса. Если бит 6 равен 0, то данные в буфере соответствуют данным в странице основной памяти. Если бит 6 равен 1, то данные в странице основной памяти отличаются от данных в буфере хотя бы одним битом.

Бит 1 в регистре статуса информирует пользователя о том включен или выключен (программным или аппаратным методом) режим защиты секторов. Значение 1 соответствует включенной защите секторов, значение 0 выключенной защите.

Бит 0 в регистре статуса информирует о размере страниц в основной памяти. Значение 1 соответствует размеру страниц в 512 байт, значение 0 размеру страниц в 528 байт.

Объем микросхемы отображается битами 5, 4, 3, 2 регистра статуса. Для микросхемы Atmel AT45DB161D значение этих 4 бит равно 1011. Десятичное значение этих бит не исчисляет объем микросхемы; биты являются комбинаторным кодом для разных объемов микросхем Atmel DataFlash. Значение битов не эквивалентно значению кода объема, выдаваемого по стандарту JEDEC в идентификаторе микросхемы. Информация об объеме микросхемы предоставляется только для обеспечения обратной совместимости.

Таблица 11.1 Формат регистра статуса| Бит 7 | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 |

| RDY/BUSY | COMP | 1 | 0 | 1 | 1 | PROTECT | PAGE SIZE |

12 Сверхнизкое энергопотребление

После подачи питания микросхема находится в режиме готовности. Команда Сверхнизкое Энергопотребление переводит микросхему в режим минимального потребления энергии. Для перехода в режим необходимо сначала активировать сигнал CS. После чего, через вывод SI, подать код команды B9H. После загрузки последнего бита команды деактивация сигнала CS включит сверхнизкое энергопотребление. Микросхема перейдёт в режим сверхнизкого энергопотребления максимум за время tEDPD. Находясь в нём, микросхема игнорирует все команды кроме команды выхода из этого режима.

Таблица 12.1 Сверхнизкое Энергопотребление| Команда | Код |

| Сверхнизкое Энергопотребление | B9H |

12.1 Выход из сверхнизкого энергопотребления

Команда Выход Из Сверхнизкого Энергопотребления переводит микросхему из режима сверхнизкого энергопотребления в стандартный режим готовности. Для выхода из режима необходимо сначала активировать сигнал CS, после чего, через вывод SI, подать код команды ABH. После подачи последнего бита команды, деактивация сигнала CS выключит режим сверхнизкого энергопотребления. Микросхема переключится в режим готовности максимум за время tRDPD. Перед тем как микросхема сможет вновь принимать команды сигнал CS должен оставаться в неактивном состоянии в течение времени tRDPD.

Таблица 12.2 Выход Из Сверхнизкого Энергопотребления| Команда | Код |

| Выход Из Сверхнизкого Энергопотребления | ABH |

13 Режим размера страницы кратного степени 2

Энергонезависимый, программируемый пользователем, конфигурационный регистр Размер Страницы Кратный Степени 2 позволяет выбрать стандартный размер страницы Atmel DataFlash(528 байт) или бинарный размер страницы (512 байт). Установить размер страницы в 512 байт можно только один раз, после того как размер страницы установлен изменить его будет нельзя. Изначально микросхемы поставляются с размером страниц установленным в 528 байт. Но есть возможность заказать поставку микросхем с размером страниц в 512 байт. Подробнее об этом говорится в разделе «Информация для заказа».

Для того чтобы активировать режим страниц размером 512 байт необходимо выполнить следующие шаги:

- запрограммировать регистр конфигурации последовательностью кодов 3DH, 2AH, 80H и A6H(см секцию 13.1).

- сбросить и подать снова питание на микросхему.

- Теперь запись в страницы проводится по 512 байт.

Если вышеперечисленные шаги по настройке размера страниц не были выполнены перед их записью, то в дальнейшем при их чтении возможно появление ошибок.

13.1 Программирование конфигурационного регистра

Как и с любой другой командой, перед программированием конфигурационного регистра на размер страницы кратный степени 2, необходимо предварительно активировать сигнал CS. После этого, в строго заданном порядке, подается 4-х байтовая последовательность кода команды 3DH, 2AH, 80H, A6H. После загрузки последнего бита последовательности для запуска процесса программирования деактивировать сигнал CS. Программирование должно закончится максимум за время tp, в течение которого Регистр Статуса будет информировать о занятости микросхемы. После завершения программирования, для установки размера страницы, необходимо выполнить сброс и подачу питания на микросхему. Если сброс питания произойдет до завершения цикла программирования, то правильная установка регистра конфигурации не гарантируется. Чтобы выяснить установлен размер страницы в 512 байт или нет, необходимо проверить бит 0 в Регистре Статуса. Если не установлен, команду можно послать повторно.

Таблица 13.1 Программирование Конфигурационного Регистра| Команда | Байт 1 | Байт 2 | Байт 3 | Байт 4 |

| Размер Страницы Кратный Степени 2 | 3DH | 2AH | 80H | A6H |

14 Чтение идентификаторов производителя и микросхемы

Конечное устройство может опознать установленную в него микросхему прочитав из неё идентификационную информацию. Метод идентификации, а также код команды соответствуют стандарту JEDEC “Методика чтения идентификаторов производителя и микросхемы для микросхем памяти с SPI-совместимым последовательным интерфейсом”. Из микросхемы можно прочесть следующее данные: присвоенный JEDEC код производителя, присвоенный производителем код микросхемы, дополнительную информацию.

Чтобы прочесть идентификаторы необходимо предварительно активировать сигнал CS и загрузить код команды 9FH. После загрузки команды, с последующими тактовыми импульсами, микросхема начнет выводить идентифицирующие данные на вывод SO. Первый выводимый байт содержит код производителя, далее следуют 2 байта с информацией по микросхеме. Четвертый байт содержит длину строки с дополнительной информацией, его значение всегда 00H и говорит о том, что дополнительная информация не предоставляется. В стандарте JEDEC говорится, что чтение длины строки и любых последующих данных не обязательно.

Деактивация сигнала CS завершит чтение идентификационных данных и переведет вывод SO в высокоимпедансное состояние. Сигнал CS можно деактивировать в любой момент, не дожидаясь полного чтения данных.

14.1 Информация о производителе и ID микросхемы

| Значение | Код назначенный JEDEC | ||||||||||

| Бит 7 | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 | ||||

| 1FH | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | Код производителя | 1FH = Atmel | |

| Значение | Код Серии | Код объема | |||||||||

| Бит 7 | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 | Код серии | 001 = Atmel DataFlash | ||

| 26H | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | Код объема | 00110 = 16-Мбит | |

| Значение | Код MLC | Версия Продукта | |||||||||

| Бит 7 | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 | Код MLC | 000=1-бит технология | ||

| 00H | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Версия | 00000 = начальная | |

| Значение | Количество байт | ||||||||||

| Бит 7 | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 | ||||

| 00H | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Количество байт | 00H = 0 байт | |

14.2 Сводка по режимам работы

Чтобы лучше описать какие и в какой момент команды можно выполнять, вышеописанные команды можно сгруппировать в 4 категории.

Группа команд А состоит из:

- Чтение страницы основной памяти

- Непрерывное чтение массива памяти

- Чтение регистра защиты сектора

- Чтение регистра блокировки сектора

- Чтение регистра защиты

Группа команд B состоит из:

- Стирание страницы

- Стирание блока

- Стирание сектора

- Стирание микросхемы

- Передача страницы основной памяти в буфер 1 (или 2)

- Сравнение страницы основной памяти с буфером 1 (или 2)

- Запись буфера 1 (или 2) в страницу основной памяти с автоматическим стиранием

- Запись буфера 1 (или 2) в страницу основной памяти без автоматического стирания

- Запись страницы основной памяти через буфер 1 (или 2)

- Автоматическая перезапись страницы

Группа команд C состоит из:

- Чтение Буфера 1 (или 2)

- Запись Буфера 1 (или 2)

- Чтение регистра статуса

- Чтение идентификаторов производителя и микросхемы

Группа команд D состоит из:

- Регистр защиты сектора от стирания

- Регистр защиты сектора от записи

- Блокировка сектора

- Программирование регистра защиты

Если выполняется команда из группы A, то запуск других команд из группы A, B, C, D запрещен. Тем не менее, вовремя выполнения самотактируемых команд из группы B, допускается запуск любой команды из группы C. Если команда из группы B работает с буфером 1, то команда из группы C должна работать с буфером 2 и наоборот. Наконец, при выполнении самотактируемых команд из группы D разрешается только команда чтения регистра статуса.

15 Таблицы команд

Таблица 15.1 Команды чтения| Команда | Код операции |

| Чтение страницы основной памяти | D2H |

| Непрерывное чтение массива(устаревшая команда) | E8H |

| Непрерывное чтение массива(низкая скорость) | 03H |

| Непрерывное чтение массива(высокая скорость) | 0BH |

| Чтение буфера 1(низкая скорость) | D1H |

| Чтение буфера 2(низкая скорость) | D3H |

| Чтение буфера 1 | D4H |

| Чтение буфера 2 | D6H |

| Команда | Код операции |

| Запись в буфер 1 | 84H |

| Запись в буфер 2 | 87H |

| Запись буфера 1 в страницу основной памяти с авто-стиранием | 83H |

| Запись буфера 2 в страницу основной памяти с авто-стиранием | 86H |

| Запись буфера 1 в страницу основной памяти без авто-стирания | 88H |

| Запись буфера 2 в страницу основной памяти без авто-стирания | 89H |

| Стирание страницы | 81H |

| Стирание блока | 50H |

| Стирание сектора | 7CH |

| Стирание микросхемы | C7H, 94H, 80H, 9AH |

| Запись страницы основной памяти через буфер 1 | 82H |

| Запись страницы основной памяти через буфер 2 | 85H |

| Команда | Код операции |

| Включить защиту сектора | 3DH+2AH+7FH+A9H |

| Выключить защиту сектора | 3DH+2AH+7FH+9AH |

| Очистить регистр защиты сектора | 3DH+2AH+7FH+CFH |

| Запись регистра защиты сектора | 3DH+2AH+7FH+FCH |

| Чтение регистра защиты сектора | 32H |

| Блокировка сектора | 3DH+2AH+7FH+30H |

| Чтение регистра блокировки сектора | 35H |

| Запись регистра защиты | 9BH+00H+00H+00H |

| Чтение регистра защиты | 77H |

| Команда | Код операции |

| Передача страницы основной памяти в буфер 1 | 53H |

| Передача страницы основной памяти в буфер 2 | 55H |

| Сравнение страницы основной памяти с буфером 1 | 60H |

| Сравнение страницы основной памяти с буфером 2 | 61H |

| Автоматическая перезапись страницы через буфер 1 | 58H |

| Автоматическая перезапись страницы через буфер 2 | 59H |

| Пониженное энергопотребление | B9H |

| Выход из пониженного энергопотребления | ABH |

| Чтение регистра статуса | D7H |

| Чтение идентификаторов производителя и микросхемы | 9FH |

| Команда | Код операции |

| Чтение буфера 1 | 54H |

| Чтение буфера 2 | 56H |

| Чтение страницы основной памяти | 52H |

| Непрерывное чтение массива памяти | 68H |

| Чтение регистра статуса(2) | 57H |

Примечания:

- Устаревшие команды не рекомендуются к применению в новых разработках

- См таблицу с историей изменений на странице 52.

Таблица 15.6 Детальное описание битов адреса для страниц кратных степени 2

| Размер страницы = 512 байт | Байт адреса | Байт адреса | Байт адреса | Дополни тельные биты |

||||||||||||||||||||||||||||||||||||

| Код команды | ре зе рв |

ре зе рв |

ре зе рв |

A 20 |

A 19 |

A 18 |

A 17 |

A 16 |

A 15 |

A 14 |

A 13 |

A 12 |

A 11 |

A 10 |

A 9 |

A 8 |

A 7 |

A 6 |

A 5 |

A 4 |

A 3 |

A 2 |

A 1 |

A 0 |

||||||||||||||||

| 03h | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | недоступно | |||||||

| 0Bh | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | 1 | |||||||

| 50h | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | x | x | x | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 53h | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 55h | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 58h | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 59h | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 60h | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 61h | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 77h | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 7Ch | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | x | x | x | A | A | A | A | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 81h | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 82h | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | недоступно | |||||||

| 83h | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 84h | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | A | A | A | A | A | A | A | A | A | недоступно | |||||||

| 85h | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | недоступно | |||||||

| 86h | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 87h | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | A | A | A | A | A | A | A | A | A | недоступно | |||||||

| 88h | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 89h | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 9Fh | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | недоступно | недоступно | недоступно | недоступно | ||||||||||||||||||||||||||||

| B9h | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | недоступно | недоступно | недоступно | недоступно | ||||||||||||||||||||||||||||

| ABh | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | недоступно | недоступно | недоступно | недоступно | ||||||||||||||||||||||||||||

| D1h | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | A | A | A | A | A | A | A | A | A | недоступно | |||||||

| D2h | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | 4 | |||||||

| D3h | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | A | A | A | A | A | A | A | A | A | недоступно | |||||||

| D4h | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | A | A | A | A | A | A | A | A | A | 1 | |||||||

| D6h | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | A | A | A | A | A | A | A | A | A | 1 | |||||||

| D7h | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | недоступно | недоступно | недоступно | недоступно | ||||||||||||||||||||||||||||

| E8h | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | x | x | x | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | 4 | |||||||

Таблица 15.7 Детальное описание битов адреса для стандартных страниц Atmel DataFlash (528 байт)

| Размер страницы = 528 байт | Байт адреса | Байт адреса | Байт адреса | Дополни тельные биты |

||||||||||||||||||||||||||||||||||||

| Код команды | ре зе рв |

ре зе рв |

ре зе рв |

PA 11 |

PA 10 |

PA 09 |

PA 07 |

PA 06 |

PA 05 |

PA 04 |

PA 03 |

PA 02 |

PA 01 |

PA 00 |

BA 9 |

BA 8 |

BA 7 |

BA 6 |

BA 5 |

BA 4 |

BA 3 |

BA 2 |

BA 1 |

BA 0 |

||||||||||||||||

| 03h | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | B | B | B | B | B | B | B | B | B | B | недоступно | |||||||

| 0Bh | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | B | B | B | B | B | B | B | B | B | B | 1 | |||||||

| 50h | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | x | x | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 53h | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 55h | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 58h | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 59h | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 60h | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 61h | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 77h | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 7Ch | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | x | x | P | P | P | P | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 81h | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 82h | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | B | B | B | B | B | B | B | B | B | B | недоступно | |||||||

| 83h | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 84h | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | B | B | B | B | B | B | B | B | B | B | недоступно | |||||||

| 85h | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | B | B | B | B | B | B | B | B | B | B | недоступно | |||||||

| 86h | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 87h | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | B | B | B | B | B | B | B | B | B | B | недоступно | |||||||

| 88h | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 89h | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | x | x | x | x | x | x | x | x | x | x | недоступно | |||||||

| 9Fh | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | недоступно | недоступно | недоступно | недоступно | ||||||||||||||||||||||||||||

| B9h | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | недоступно | недоступно | недоступно | недоступно | ||||||||||||||||||||||||||||

| ABh | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | недоступно | недоступно | недоступно | недоступно | ||||||||||||||||||||||||||||

| D1h | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | B | B | B | B | B | B | B | B | B | B | недоступно | |||||||

| D2h | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | B | B | B | B | B | B | B | B | B | B | 4 | |||||||

| D3h | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | B | B | B | B | B | B | B | B | B | B | недоступно | |||||||

| D4h | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | B | B | B | B | B | B | B | B | B | B | 1 | |||||||

| D6h | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | x | x | x | x | x | x | x | x | x | x | x | x | x | x | B | B | B | B | B | B | B | B | B | B | 1 | |||||||

| D7h | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | недоступно | недоступно | недоступно | недоступно | ||||||||||||||||||||||||||||

| E8h | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | x | x | P | P | P | P | P | P | P | P | P | P | P | P | B | B | B | B | B | B | B | B | B | B | 4 | |||||||

16 Состояние при включении/сбросе

При первичном включении или при выходе из состояния сброса микросхема по умолчанию переходит в режим 3. Выход SO устанавливается в высокоимпедансное состояние, а для начала верной команды требуется переход сигнала CS из высокого в низкое состояние. Режим 3 или 0 автоматически выбирается отрицательным фронтом CS при неактивном тактовом сигнале.

16.1 Временные ограничения на включение/сброс

При включении микросхема должна быть неактивна до тех пор, пока напряжение питания не достигнет значения VCC(min) и после этого не пройдет время tVCSL. Встроенная схема сброса удерживает микросхему в состоянии сброс пока напряжение питания не превысит порогового значения VPOR. В это время все функции отключены и микросхема не отвечает на любые команды. Чтобы микросхема смогла выполнять операции чтения необходимо, после достижения VCC значения VCC(min), выдержать паузу длительностью tVCSL.

Аналогично, чтобы микросхема смогла выполнять операции записи/стирания необходимо, по достижению VCC значения VPOR, выдержать паузу длительностью tPUW.

После подачи питания микросхема находится в состоянии готовности.

Таблица 16.1 Временные ограничения на включение/сброс| Обозначение | Параметр | Мин | Типич | Макс | Един |

| tVCSL | Задержка от VCC(min) до активного CS | 70 | мкс | ||

| tPUW | Задержка после подачи питания, перед записью | 20 | мс | ||

| VPOR | Напряжение сброса по подаче питания | 1.5 | 2.5 | В |

17 Системные требования

Последовательный интерфейс RapidS компании Atmel управляется выводами SCK, SI и CS. Эти сигналы должны иметь монотонные фронты и не иметь помех. Чрезмерный шум или звон на выводах может привести к неверной работе. Дорожки на печатной плате должны иметь минимальную длину или корректно завершаться. Для фильтрации помех на выводы можно установить развязывающие конденсаторы.

С ростом сложности систем, все более необходимым становится применение стабилизаторов напряжения у которых ключевым элементом является выходной ток. Максимальный ток микросхемой Atmel DataFlash потребляется во время операций записи и стирания. Стабилизатор должен поддерживать эти максимальные значения. В противном случае возникнет нехватка тока. Помимо увеличения помех, нехватка тока во время программирования или стирания может привести к искажению данных.

18 Электрические характеристики

Таблица 18.1 Максимальные значения| Рабочая температура | -55°C до +125°С | Примечание: |

Внешнее воздействие за указанными пределами может привести к необратимой порче микросхемы. Нахождение в граничных условиях длительное время может повлиять на надежность микросхемы. Граничные напряжения подразумевают короткое время их действия и не гарантируют длительную работу микросхемы на этих уровнях. |

| Температура хранения | -65°C до +150°C | ||

| Входное напряжение на всех входах (кроме VCC, но включая NC) по отношению к земле | -0.6В до 6.25В | ||

| Выходное напряжение по отношению к земле | -0.6В до VCC+0.6В |

| Atmel AT45DB161D (2.5B) | Atmel AT45DB161D | |

| Температурный диапазон(корпуса) | -40°C до +85°C | -40°C до +85°C |

| Напряжение питания VCC | 2.5В до 3.6В | 2.7В до 3.6В |

| Обозн | Параметр | Условия | Мин | Типич | Макс | Един. |

| IDP | Потребляемый ток в режиме сверхнизкого энергопотребления | CS, RESET, WP = VIH, на входах уровни CMOS | 15 | 25 | мкA | |

| ISB | Потребляемый ток в режиме готовности | CS, RESET, WP = VIH, на входах уровни CMOS | 25 | 50 | мкA | |

| ICC1(1) | Потребляемый ток, операция чтения | f=20МГц; IOUT=0мA; VCC=3.6В | 7 | 10 | мA | |

| f=33МГц; IOUT=0мA; VCC=3.6В | 8 | 12 | мA | |||

| f=50МГц; IOUT=0мA; VCC=3.6В | 10 | 14 | мA | |||

| f=66МГц; IOUT=0мA; VCC=3.6В | 11 | 15 | мA | |||

| ICC2 | Потребляемый ток, операция стирания/записи | VCC=3.6В | 12 | 17 | мA | |

| ILI | Входной втекающий ток | VIN=CMOS уровни | 1 | мкA | ||

| ILO | Выходной ток утечки | VI/O=CMOS уровни | 1 | мкA | ||

| VIL | Напряжение низкого уровня (вход) | VCC*0.3 | В | |||

| VIH | Напряжение высокого уровня (вход) | VCC*0.7 | В | |||

| VOL | Напряжение низкого уровня (выход) | IOL=1.6мA;VCC=2.7В | 0.4 | В | ||

| VOH | Напряжение высокого уровня (выход) | IOH=100мкA | VCC-0.2В | В |

| Примечания: | 1. ICC1 во время чтения буфера максимум 20мA @ 20МГц 2. Входы (SI, SCK, CS, WP и RESET) гарантированно совместимы с 5В. |

| Обозн | Параметр | AT45DB161D (версия 2.5В) |

AT45DB161D | Един | ||||

| Мин | Типич | Макс | Мин | Типич | Макс | |||

| fSCK | Частота SCK | 50 | 66 | МГц | ||||

| fCAR1 | Частота SCK при непрерывном чтении массива | 50 | 66 | МГц | ||||

| fCAR2 | Частота SCK при непрерывном чтении массива (низкая скорость) | 33 | 33 | МГц | ||||

| tWH | Длительность высокого SCK | 6.8 | 6.8 | нс | ||||

| tWL | Длительность низкого SCK | 6.8 | 6.8 | нс | ||||

| tSCKR(1) | Скорость нарастания SCK | 0.1 | 0.1 | В/нс | ||||

| tSCKF(1) | Скорость спада SCK | 0.1 | 0.1 | В/нс | ||||

| tCS | Минимальная длительность высокого CS | 50 | 50 | нс | ||||

| tCSS | Время установки CS | 5 | 5 | нс | ||||

| tCSH | Время удержания CS | 5 | 5 | нс | ||||

| tCSB | Задержка между высоким CS и низким RDY/BUSY | 100 | 100 | нс | ||||

| tSU | Время установки входных данных | 2 | 2 | нс | ||||

| tH | Время удержания входных данных | 3 | 3 | нс | ||||

| tHO | Время удержания выхода | 0 | 0 | нс | ||||

| tDIS | Время отключения выхода | 27 | 35 | 27 | 35 | нс | ||

| tV | Задержка корректных данных | 8 | 6 | нс | ||||

| tWPE | Переход с низкого WP в включение защиты | 1 | 1 | мкс | ||||

| tWPD | Переход с высокого WP в отключение защиты | 1 | 1 | мкс | ||||

| tEDPD | Переход с высокого CS в режим сверхнизкого потребления | 3 | 3 | мкс | ||||

| tRDPD | Переход с высокого CS в режим готовности | 35 | 35 | мкс | ||||

| tXFR | Время передачи страницы в буфер | 200 | 200 | мкс | ||||

| tCOMP | Время сравнения страницы с буфером | 200 | 200 | мкс | ||||

| tEP | Время стирания и записи страницы (512/528 байт) | 17 | 40 | 17 | 40 | мс | ||

| tP | Время записи страницы (512/528 байт) | 3 | 6 | 3 | 6 | мс | ||

| tPE | Время стирания страницы (512/528 байт) | 15 | 35 | 15 | 35 | мс | ||

| tBE | Время стирания блока (4096/4224 байт) | 45 | 100 | 45 | 100 | мс | ||

| tSE | Время стирания сектора (131072/135168 байт) | 0.7 | 1.3 | 0.7 | 1.3 | с | ||

| tCE | Время стирания микросхемы | 12 | 25 | 12 | 25 | с | ||

| tRST | Длительность импульса RESET | 10 | 10 | мкс | ||||

| tREC | Время выхода из RESET | 1 | 1 | мкс | ||||

Примечания: 1. Значения основаны на спецификации к микросхеме и при производстве не тестируются.

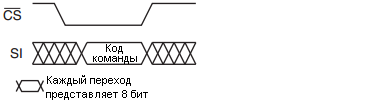

21 Временные диаграммы сигналов

Ниже представлены 6 временных диаграмм. На диаграмме 1 показан случай, когда сигнал SCK находится в низком уровне во время положительного фронта сигнала CS. На диаграмме 2 показан случай, когда сигнал SCK находится в высоком уровне во время отрицательного фронта сигнала CS. В обоих случаях значение на выходе SO становится корректным во время низкого уровня сигнала SCK (длительность низкого уровня SCK указана как tWL). Временные диаграммы 1 и 2 соответствуют последовательному интерфейсу Atmel RapidS, но для частот до 66МГц. Кроме того, диаграммы 1 и 2 совместимы соответственно с режимом SPI 0 и 3.

На диаграммах 3 и 4 представлены обобщенные временные диаграммы последовательного интерфейса RapidS. Они схожи с диаграммами 1 и 2, за исключением того что на сигнал SO не накладывается ограничение корректности во время периода длительностью tWL. Эти диаграммы актуальны для всего диапазона скоростей интерфейса RapidS (максимальная частота 66МГц).

21.1 Диаграмма 1. Совместимая с режимом SPI 0(для частот до 66МГц)

21.2 Диаграмма 2. Совместимая с режимом SPI 3(для частот до 66МГц)

21.3 Диаграмма 3. Atmel RapidS режим 0(FMAX = 66МГц)

21.4 Диаграмма 4. Atmel RapidS режим 3(FMAX = 66МГц)

21.5 Применение Atmel RapidS

Чтобы получить преимущество от возможности Atmel RapidS работать на более высоких скоростях необходимо при передаче данных по последовательной шине полностью задействовать тактовый импульс. Atmel DataFlash разработана таким образом, что данные всегда выгружаются по отрицательному фронту SCK, а загружаются по положительному SCK.

Тактовый импульс будет полностью задействован если при выдаче данных из DataFlash по отрицательному фронту SCK контроллер, чтобы эти данные зафиксировать, будет ждать следующего отрицательного фронта. Аналогично, контроллер должен выдавать данные на положительном фронте SCK для того чтобы позволить DataFlash получить их на следующем положительном фронте SCK.

MOSI = выход ведущего, вход ведомого (Master Out Slave In)

MISO = вход ведущего, выход ведомого (Master In Slave Out)

Ведущим является контроллер, ведомым Atmel DataFlash.

Ведущий всегда выдает данные по положительному фронту SCK и принимает по отрицательному фронту SCK.

Ведомый всегда выдаёт данные по отрицательному фронту SCK и принимает по положительному фронту SCK.

Рисунок 21.1 Режим Atmel RapidS

Ведущий, по положительному фронту SCK, выдает первый бит байта MOSI

Ведомый, на следующем положительном фронте SCK, принимает первый бит MOSI

Ведущий, на этом-же положительном фронте SCK, выдает второй бит MOSI

Последний бит в MOSI выдан ведущим

Последний бит в MOSI получен ведомым

Ведомый выдает первый бит в байте SO

Ведущий принимает первый бит байта SO

Ведомый выдает второй бит в байте SO

Ведущий загружает последний бит байта SO

21.6 Диаграмма сброса