24AA256/24LC256/24FC256 - 256Кбит последовательная I2C EEPROM |

скачать

скачатьв pdf |

Таблица выбора микросхем

| Шифр компонента | Диапазон Vcc | Макс. тактовая частота | Темп. диапазон |

| 24AA256 | 1.7 – 5.5В | 400кГц(1) | I |

| 24LC256 | 2.5 – 5.5В | 400кГц | I, E |

| 24FC256 | 1.7 – 5.5В | 1 МГц(2) | I |

2: 400кГц для Vcc < 2.5В

Характеристики:

|

|

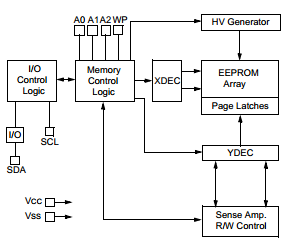

Описание:24AA256/24LC256/24FC256 это электрически стираемое ППЗУ с организацией памяти 32Кх8 (256 Кбит), работающее в широком диапазоне питающих напряжений(1.7В-5.5В). Создано для применения в передовых низко-потребляющих системах(связи, сбора данных). Предоставляет возможность страничной записи данных размером до 64 байт. Поддерживается как последовательное, так и произвольное чтение данных. Адресные выводы позволяют организовать единое адресное пространство до 2-х Мбит, разместив на одной шине до 8-ми микросхем. Микросхема доступна в 8-ми выводных корпусах DIP, SOIC, TSSOP, MSOP и DFN. А 24AA256 ещё и в 8-ми выводном корпусе размером с кристалл. |

Блок-схема:

|

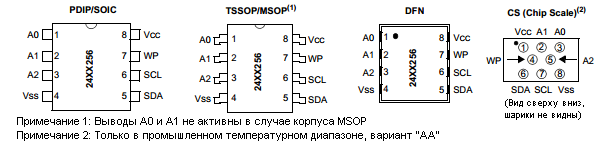

Типы корпусов:

1.0 Электрические параметры

Максимально допустимые значения(†)

Vcc..............................................................................................6.5В

Напряжение на выводах относительно Vss...........................-0.6В до Vcc+1.0В

Температура хранения............................................................-65ºС до +150ºС

Рабочая температура..............................................................-40ºС до +125ºС

Защита от электростатического разряда...............................≥4кВ.

†Примечание: Внешнее воздействие, выходящее за границы максимально допустимых, может привести к необратимому повреждению микросхемы. Работа в указанных условиях, или условиях, превышающих указанные в перечне рабочих величин, не подразумевается. Воздействие указанных максимально допустимых значений может повлиять на надёжность микросхемы.

Таблица 1-1: Параметры по постоянному току

| Параметры по постоянному току |

Электрические характеристики: Пром.(I): Vcc = +1.7В до 5.5В TA = -40ºC до +85ºС Автомоб.(E): Vcc = +2.5В до 5.5В TA = -40ºС до +125ºС |

|||||

| Парам. | Обознач. | Характеристика | Мин. | Макс. | Единица | Условия |

|

|

- | Выводов A0, A1, A2, SCL, SDA и WP: | - | - | - | - |

| D1 | VIH | Напряжение высокого уровня (вход) | 0.7VCC | - | В | - |

| D2 | VIL | Напряжение низкого уровня (вход) | - |

0.3VCC 0.2VCC |

В В |

VCC≥ 2.5В VCC< 2.5В |

| D3 | VHYS | Гистерезис для входов с триггерами Шмитта (SDA, SCL) | 0.05VCC | - | В | VCC≥ 2.5В (Примечание) |

| D4 | VOL | Напряжение низкого уровня (выход) | - | 0.40 | В |

IOL= 3.0 mА @ VCC = 4.5В IOL= 2.1 mА @ VCC = 2.5В |

| D5 | ILI | Входной ток утечки | - | ±1 | μА |

VIN = VSS или VCC, WP = VSS VIN = VSS или VCC, WP = VCC |

| D6 | ILO | Выходной ток утечки | - | ±1 | μА | VOUT=VSS или VCC |

| D7 | CIN, COUT | Ёмкость выводов | - | 10 | пФ |

VCC=5.0В (Примечание) TA=25ºC, FCLK=1МГц. |

| D8 | ICCЧтение | Ток потребления | - | 400 | μА | VCC=5.5В, SCL = 400кГц |

| ICCЗапись | - | 3 | mА | VCC=5.5В | ||

| D9 | ICCS | Ток потребления в режиме ожидания | - | 1 | μА |

TA = -40ºC до +85ºC SCL=SDA=VCC=5.5B A0, A1, A2, WP = VSS |

| - | 5 | μА |

TA = -40ºC до +125ºC SCL=SDA=VCC=5.5B A0, A1, A2, WP = VSS |

|||

Примечание: Этот параметр проверяется время от времени.

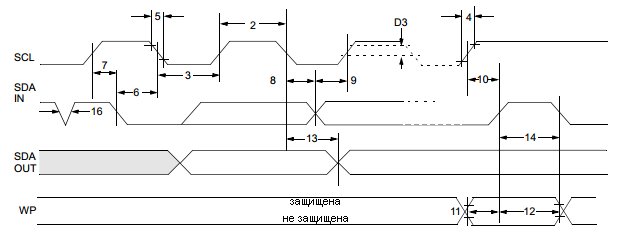

Таблица 1-2: Параметры по переменному току

| Параметры по переменному току |

Электрические характеристики: Пром.(I): Vcc = +1.7В до 5.5В TA = -40ºC до +85ºС Автомоб.(E): Vcc = +2.5В до 5.5В TA = -40ºС до +125ºС |

|||||

| Парам. | Обознач. | Характеристика | Мин. | Макс. | Единица | Условия |

| 1 | FCLK | Частота тактового сигнала |

- - - - |

100 400 400 1000 |

кГц |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC < 2.5В 24FC256 2.5В ≤ VCC ≤ 5.5В 24FC256 |

| 2 | THIGH | Длительность высокого состояния тактового импульса |

4000 600 600 500 |

- - - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC < 2.5В 24FC256 2.5В ≤ VCC ≤ 5.5В 24FC256 |

| 3 | TLOW | Длительность низкого состояния тактового импульса |

4700 1300 1300 500 |

- - - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC < 2.5В 24FC256 2.5В ≤ VCC ≤ 5.5В 24FC256 |

| 4 | TR | Время нарастания для SDA и SCL (примечание 1) |

- - - |

1000 300 300 |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC ≤ 5.5В 24FC256 |

| 5 | TF | Время спада для SDA и SCL |

- - |

300 100 |

нс |

Для всех, кроме 24FC256 1.7В ≤ VCC ≤ 5.5В 24FC256 |

| 6 | THD:STA | Время удержания сигнала СТАРТ |

4000 600 600 250 |

- - - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC < 2.5В 24FC256 2.5В ≤ VCC ≤ 5.5В 24FC256 |

| 7 | TSU:STA | Время установки сигнала СТАРТ |

4700 600 600 250 |

- - - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC < 2.5В 24FC256 2.5В ≤ VCC ≤ 5.5В 24FC256 |

| 8 | THD:DAT | Время удержания данных при чтении | 0 | - | нс | (Примечание 2) |

| 9 | TSU:DAT | Время установки данных при чтении |

250 100 100 |

- - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC ≤ 5.5В 24FC256 |

| 10 | TSU:STO | Время установки сигнала СТОП |

4000 600 600 250 |

- - - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC < 2.5В 24FC256 2.5В ≤ VCC ≤ 5.5В 24FC256 |

| 11 | TSU:WP | Время установки WP |

4000 600 600 |

- - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC ≤ 5.5В 24FC256 |

| 12 | THD:WP | Время удержания WP |

4700 1300 1300 |

- - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC ≤ 5.5В 24FC256 |

| 13 | TAA | Время от тактового импульса до корректных данных на выходе |

- - - - |

3500 900 900 400 |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC < 2.5В 24FC256 2.5В ≤ VCC ≤ 5.5В 24FC256 |

| 14 | TBUF | Время перед началом обмена, в течении которого шина должна быть свободной. |

4700 1300 1300 500 |

- - - - |

нс |

1.7В ≤ VCC < 2.5В 2.5В ≤ VCC ≤ 5.5В 1.7В ≤ VCC < 2.5В 24FC256 2.5В ≤ VCC ≤ 5.5В 24FC256 |

| 15 | TOF | Время спада от мин. VIH до макс. VIL (CB ≤ 100 пФ) | 10 + 0.1CB |

250 250 |

нс | Для всех, кроме 24FC256 (Примечание 1) |

| 16 | TSP | Выброс на SDA и SCL, подавляемый входным фильтром. | - | 50 | нс | Для всех, кроме 24FC256 (Примечания 1 и 3) |

| 17 | TWC | Время записи байта или страницы | - | 5 | мс | - |

| 18 | - | износоустойчивость | 1 000 000 | - | циклов | Страничный режим, 25ºC, 5.5В (Примечание 4) |

Примечания:

- 100% не тестируется. CB = общая ёмкость линии в пФ.

- Для того чтобы исключить непреднамеренную генерацию сигналов STOP или START, микросхема в режиме передатчика гарантирует минимальную внутреннюю задержку(300нс), которая перекроет область неопределенности на спаде SCL.

- Комбинация из TSP и VHYS даётся в связи с новыми триггерами Шмитта, которые обеспечивают улучшенное подавление выбросов. Поэтому, в условиях нормальной работы, указание параметра TIне требуется.

- Этот параметр не тестируется, но гарантируется описанием. Для оценки износоустойчивости в конкретном применении, пожалуйста обратитесь к Total Endurance Model на сайте www.microchip.com

Рисунок 1-1: Временная диаграмма шины

2.0 Описание выводов

В таблице 2-1 представлено краткое описание выводов.Таблица 2-1: Назначение выводов

| Название | PDIP 8 | SOIC 8 | TSSOP 8 | MSOP 8 | DFN 8 | CS | Назначение |

| A0 | 1 | 1 | 1 | - | 1 | 3 | Настраиваемый сигнал выбора микросхемы |

| A1 | 2 | 2 | 2 | - | 2 | 2 | |

| (NC) | - | - | - | 1, 2 | - | - | Не соединяется |

| A2 | 3 | 3 | 3 | 3 | 3 | 5 | Сигнал выбора микросхемы |

| Vss | 4 | 4 | 4 | 4 | 4 | 8 | Земля |

| SDA | 5 | 5 | 5 | 5 | 5 | 6 | Данные |

| SCL | 6 | 6 | 6 | 6 | 6 | 7 | Тактовый сигнал |

| (NC) | - | - | - | - | - | - | Не соединяется |

| WP | 7 | 7 | 7 | 7 | 7 | 4 | Вход защиты от записи |

| Vcc | 8 | 8 | 8 | 8 | 8 | 1 |

от +1.7В до 5.5В (24AA256) от +2.5В до 5.5В (24LC256) от +1.7В до 5.5В (24FC256) |

2.1 Адресные выводы A0, A1, A2

Уровни на этих выводах сравниваются с соответствующими битами в адресе ведомого устройства. И в случае их совпадения микросхема - активируется.

В варианте с корпусом MSOP выводы A0 и A1 не соединены.

Используя комбинации адресных выводов, к одной шине можно подключить до 8 микросхем(2 для случая MSOP). Эти выводы должны подключаться либо к Vss либо к Vcc.

В большинстве случаев, адресные выводы A0, A1 и A2 жестко соединены с логическим '0' или '1'. В приложениях, где эти выводы управляются микроконтроллером или другим программируемым устройством, адресные выводы должны быть установлены в логические '0' или '1' до того как начнётся работа с микросхемой.

2.2 Линия данных (SDA)

Это двунаправленный вывод, используется для передачи адреса и данных в/из микросхемы. Является выводом с открытым стоком. Поэтому, для вывода SDA необходима установка подтягивающего к Vcc резистора(10кОм для 100кГц, 2кОм для 400кГц и 1МГц). Во время передачи данных изменение сигнала SDA допускается только во время низкого уровня SCL. Изменения во время высокого уровня SCL указывают на сигнал START или STOP.

2.3 Линия тактирования (SCL)

Вывод используется для синхронизации передачи данных из/в микросхему.

2.4 Защита записи (WP)

Этот вывод должен быть подключен либо к Vss либо к Vcc. Если соединен с Vss операции записи разрешены. Если соединен с Vcc операции записи запрещены, на операции чтения состояние вывода не влияет.

3.0 Функциональное описание

Микросхема 24XX256 имеет двунаправленную, 2-х проводную шину обмена данными. Устройство, посылающее данные в шину, называется передатчиком, а принимающее - приёмником. Шиной управляет ведущее устройство, которое генерирует тактовый сигнал (SCL), контролирует доступ к шине и генерирует сигналы START и STOP. 24XX256 может работать только в режиме ведомого. Ведущий и ведомый могут работать и как передатчик, и как приёмник, но активный режим задаётся ведущим устройством.

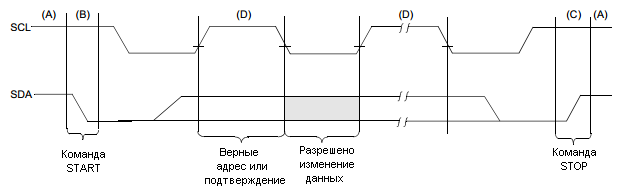

4.0 Описание шины

Определён следующий протокол шины:- Передача данных может быть начата только если шина свободна.

- Во время передачи данных, при высоком уровне на линии тактирования, линия данных должна быть в стабильном состоянии. Изменения на линии данных, при высоком уровне на линии тактирования, будут восприняты как сигнал START или STOP.

4.1 Шина свободна (A)

Линия данных и тактирования одновременно находятся в высоком состоянии.

4.2 Начало передачи данных (B)

Переход линии SDA из высокого состояния в низкое, при высоком состоянии на линии SCL, устанавливает сигнал START. Все команды должны предваряться сигналом START.

4.3 Конец передачи данных (C)

Переход линии SDA из низкого состояния в высокое, при высоком состоянии на линии SCL, устанавливает сигнал STOP. Все операции должны завершаться сигналом STOP.

4.4 Верные данные (D)

Линия данных находится в этом состоянии, если был подан сигнал

START и кроме того, на протяжении высокого уровня линии SCL, линия SDA

стабильна.

Данные на линии SDA должны изменяться во время низкого периода

тактового сигнала. Одному тактовому импульсу соответствует один бит данных.

Каждый сеанс передачи данных начинается сигналом START и завершается сигналом

STOP. Количество байт данных, переданных между START и STOP, задаётся ведущим

устройством.

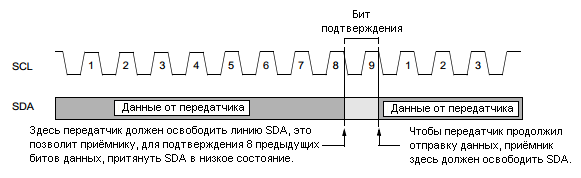

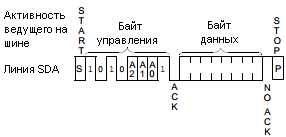

4.5 Подтверждение

Каждый адресованный приёмник обязан подтверждать приём каждого байта сигналом подтверждения. Ведущее устройство должно генерировать дополнительный тактовый импульс, к которому привязан бит подтверждения.

Примечание: 24XX256 не генерирует битов подтверждения при активном внутреннем цикле программирования.

Устройство, которое подтверждает, должно удерживать SDA в стабильном низком состоянии на время высокого уровня такта подтверждения. Конечно, необходимо учитывать время установки и время удержания. Во время чтения, ведущее устройство сигнализирует ведомому о завершении обмена данными путём не подтверждения последнего байта, выданного ведомым. В итоге ведомый сохранит линию данных в высоком состоянии, что позволит ведущему подать сигнал STOP.

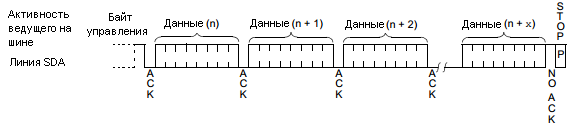

Рисунок 4-1:Порядок передачи данных по последовательной шине

Рисунок 4-2:Диаграмма подтверждения

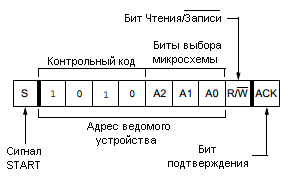

5.0 Адресация микросхем

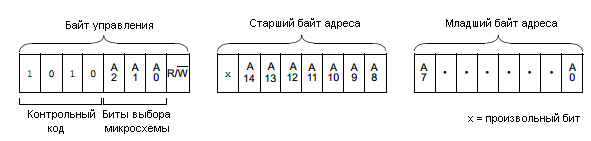

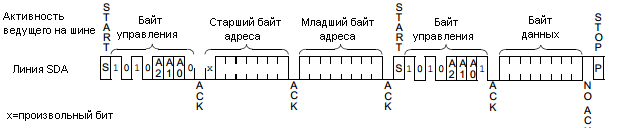

Рисунок 5-1: Формат байта управления

Байт управления —

байт, идущий от мастера сразу после сигнала START (Рисунок 5.1). Байт

управления состоит из 4-х битного контрольного кода. Для операций

чтения и записи в микросхемах 24XX256 он равен '1010'. Следующие три

бита являются битами выбора микросхемы (A2, A1, A0). Они позволяют

использовать на одной шине до 8 микросхем 24XX256 и применяются для

выбора микросхемы, к которой будет произведён доступ. Биты выбора

должны соответствовать логическим уровням на соответствующих выводах

A2, A1 и A0 ответного устройства. Они являются старшими значащими

битами в адресном слове.

Байт управления —

байт, идущий от мастера сразу после сигнала START (Рисунок 5.1). Байт

управления состоит из 4-х битного контрольного кода. Для операций

чтения и записи в микросхемах 24XX256 он равен '1010'. Следующие три

бита являются битами выбора микросхемы (A2, A1, A0). Они позволяют

использовать на одной шине до 8 микросхем 24XX256 и применяются для

выбора микросхемы, к которой будет произведён доступ. Биты выбора

должны соответствовать логическим уровням на соответствующих выводах

A2, A1 и A0 ответного устройства. Они являются старшими значащими

битами в адресном слове.

Для микросхем в корпусе MSOP выводы A0 и A1 не активны. Поэтому при адресации биты A1 и A0 должны быть установлены в 0, а к одной шине могут быть подключены только две микросхемы 24XX256 в корпусе MSOP.

Последний бит в управляющем слове задаёт тип выполняемой операции. Если бит установлен в 1, выбирается операция чтения. Если установлен в 0, выбирается операция записи.

Следующие два байта задают адрес первого байта данных(рисунок 5-2). Задействованы только биты A14-A0, значение остальных может быть произвольным. Первыми передаются старшие адресные биты.

Сразу после подачи сигнала START, микросхема 24XX256 начинает отслеживать линию SDA на предмет передачи контрольного кода микросхемы. По получении кода '1010' и соответствующих битов выбора микросхемы, ведомая микросхема выдаёт на линию SDA сигнал подтверждения. В зависимости от состояния бита R/W, 24XX256 включит режим чтения или записи.

Рисунок 5-2: Назначение битов в адресной последовательности

5.1 Режим сплошной адресации нескольких микросхем

Биты выбора микросхемы A2, A1, A0 могут быть применены для расширения непрерывного адресного пространства до 2-х Мбит путём подключеня к одной шине до 8-ми микросхем 24XX256. В этом случае программное обеспечение может использовать адресный бит A0 в качестве бита адреса A15; A1 в качестве бита адреса A16; и A2 в качестве бита адреса A17. Непрерывное чтение через границы микросхем не допускается.

Для микросхем в корпусе MSOP можно объединить 2 микросхемы, которые образуют 512Кбит адресного пространства. В этом случае программное обеспечение использует бит A2 в качестве адресного бита A17. Биты A0 (A15) и A1(A16) в байте управления должны быть установлены в 0.

6.0 Операции записи

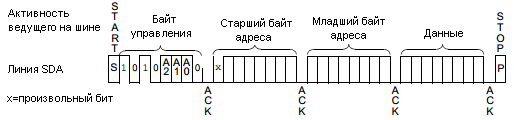

6.1 Запись байта

Ведущим, сразу после подачи сигнала START, на шину подаются контрольный код(4 бита), выбор микросхемы(3 бита) и бит R/W(установленный в 0). Эта последовательность информирует ведомое устройство о том, что после выдачи им сигнала подтверждения, будет передаваться старший байт адреса, который должен быть помещен в старший байт внутреннего счётчика адреса микросхемы 24XX256. Следующий за ним байт будет младшим адресным байтом. После подтверждения младшего адресного байта, мастер посылает слово данных, которое будет записано в адресуемую ячейку памяти. 24XX256 выдаёт подтверждение на слово данных, в ответ на которое ведущий подаёт сигнал STOP. Этим запускается внутренний цикл записи. Во время активного цикла записи, 24XX256 не выдаёт сигналов подтверждения (рисунок 6-1). Если будет совершена попытка записи в массив во время высокого состояния вывода WP, микросхема выдаст подтверждение на команду записи, но цикл записи не выполнится и микросхема сразу начнёт приём следующей команды. После выполнения команды записи байта, внутренний счётчик адреса будет указывать на следующий за только что записанным байт.

Примечание: Если выполняется запись менее 64-х байт, то вместе с записываемыми данными, произойдёт обновление и оставшихся байт страницы. Другими словами цикл записи выполняется по всей странице, вот почему износоустойчивость микросхемы указана для страниц.

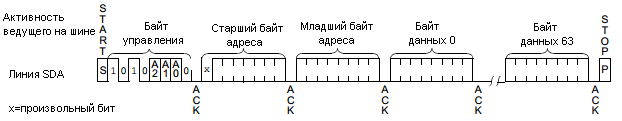

6.2 Страничная запись

Запись контрольного байта, адресного слова и первого байта данных в 24XX256 выполняются точно также как и при записи одного байта. Отличие в том что вместо подачи сигнала STOP, ведущее устройство передаёт до 63-х дополнительных байт, которые временно размещаются во внутреннем страничном буфере и будут записаны в память сразу после подачи сигнала STOP. По приёму каждого слова происходит увеличение на 1 младших 6 битов адресного указателя. Если ведущее устройство до подачи сигнала STOP передаст более 64 байт, адресный указатель зациклится и ранее принятые данные будут перезаписаны. Как и в случае одного байта, приём сигнала STOP запустит внутренний цикл записи (рисунок 6-2). Если будет совершена попытка записи в массив во время высокого состояния вывода WP, микросхема выдаст подтверждение на команду записи, но цикл записи не выполнится и микросхема сразу начнёт приём следующей команды.

6.3 Защита от записи

Вывод WP, если он притянут к Vcc, позволяет пользователю защитить от записи весь массив (0000-7FFF). Защита отключена если вывод притянут к Vss. Состояние вывода WP анализируется только во время сигнала STOP, поданного для команды записи. Изменение состояния WP после сигнала STOP не оказывает влияния на выполнение цикла записи.

Примечание: Операции страничной записи действуют только на байты в пределах одной физической страницы, независимо от того сколько байт в действительности передано. Начало физической страницы кратно размеру буфера страницы (или размеру страницы), конец находится по адресам, кратным размеру буфера страницы минус один. Если команда страничной записи попытается пересечь границу физической страницы, то вместо ожидаемой записи в следующую страницу, произойдет переход к началу текущей страницы (с перезаписью хранящихся в ней данных). Поэтому программное обеспечение должно предотвращать пересечение границ во время страничной записи.

Рисунок 6-1: Запись байта

Рисунок 6-2: Запись страницы

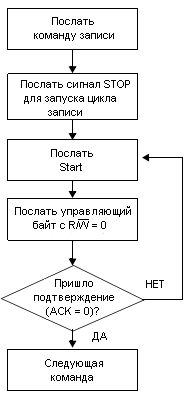

7.0 Опрос подтверждения

| Микросхема не выдаёт сигнала подтверждения во время выполнения внутреннего цикла записи, что можно использовать для определения его завершения. Сразу, после подачи ведущим сигнала STOP для команды записи, микросхема запускает цикл записи с внутренним тактированием. После этого можно начинать опрос сигнала ACK. Ведущий подаёт сигнал START и контрольный байт с активной командой записи(R/W = 0). Если микросхема всё ещё выполняет внутренний цикл, то сигнала ACK не будет и необходимо вновь подать сигнал START и контрольный байт. Если цикл завершен, микросхема выдаст ACK, а ведущий может отправить следующую команду записи или чтения. На рисунке 7-1 представлена соответствующая диаграмма. |

Рисунок 7.1 |

8.0 Операции чтения

Операции чтения запускаются во многом схожим с операциями записи образом, отличие в бите R/W управляющего байта, который должен быть установлен в '1'. Есть три основных типа операций чтения: чтение по текущему адресу, произвольное чтение и последовательное чтение.

8.1 Чтение по текущему адресу

В 24XX256 имеется встроенный счётчик адреса, хранящий увеличенный на 1 адрес обращения последней операции. К примеру, если последняя операция чтения обращалась к адресу 'n', то следующая операция чтения по текущему адресу обратится к адресу 'n+1'. Приняв управляющий байт с битом R/W установленным в '1', 24XX256 выдаёт сигнал подтверждения и передаёт 8-ми битное слово данных. Мастер вместо подтверждения приёма должен сгенерировать сигнал STOP, после которого 24XX256 прекратит обмен (рисунок 8-1).

Рисунок 8-1: Чтение по текущему адресу

8.2 Произвольное чтение

Операции произвольного чтения позволяют ведущему получить доступ к любому месту памяти в произвольном порядке. Для их выполнения необходимо предварительно установить адресный указатель. Для этого отсылаем команду записи (бит R/W установлен в '0') и адресное слово. Как только будет получено подтверждение на отправленное адресное слово, ведущий вновь генерирует сигнал START. Сигнал START завершит операцию записи, но после установки адресного указателя. После этого ведущий вновь посылает управляющий байт, но с битом R/W установленным в '1'. 24XX256 выдаст сигнал подтверждения и пошлёт 8-ми битное слово данных. Ведущий не подтверждает приём, генерирует сигнал STOP по которому 24XX256 прекращает передачу (рисунок 8-2). После выполнения команды произвольного чтения, адресный указатель будет направлен на адрес, следующий за только что прочитанным.

Рисунок 8-2:Произвольное чтение

8.3 Последовательное чтение

Последовательное чтение запускается точно так же как и произвольное, за исключением того что после передачи 24XX256 первого байта данных, ведущий, вместо сигнала STOP, генерирует сигнал подтверждения. Это подтверждение предписывает 24XX256 послать следующее адресуемое 8-ми битное слово (рисунок 8-3). После приёма последнего читаемого байта, ведущий должен сгенерировать вместо сигнала подтверждения сигнал STOP. Последовательное чтение доступно благодаря, внутреннему для 24XX256 счётчику адреса, который увеличивается на один после выполнения каждого чтения. Он позволяет последовательно прочесть содержимое всей памяти за одну операцию. Если послать сигнал подтверждения на байт с адресом 7FFF, то значение адресного указателя автоматически перейдёт с 7FFF на 0000.

Рисунок 8-3:Последовательное чтение